Intel 8086

O 8086[1] (também chamado de iAPX 86)[2] é um chip microprocessador de 16 bits lançado pela Intel em 8 de junho de 1978,[3] após o início de seu desenvolvimento no começo de 1976.[4] Foi sucedido pelo Intel 8088 em 1979,[5] que era um chip ligeiramente modificado com um barramento de dados externo de 8 bits (permitindo o uso de circuitos integrados de suporte mais baratos e em menor número).[nota 1]

O 8086 deu origem à arquitetura x86, que eventualmente se tornou a linha de processadores de maior sucesso da Intel. Em 5 de junho de 2018, a Intel lançou uma CPU de edição limitada para comemorar o 40º aniversário do Intel 8086, chamada Intel Core i7-8086K.[3]

Histórico

Contexto

Em 1972, a Intel lançou o 8008, o primeiro microprocessador de 8 bits da Intel.[nota 2] Ele implementava um conjunto de instruções projetado pela Datapoint Corporation para terminais CRT programáveis, que também se mostrou bastante versátil. O dispositivo necessitava de vários circuitos integrados adicionais para produzir um computador funcional, em parte devido ao fato de estar encapsulado em um pequeno "pacote de memória" de 18 pinos, o que inviabilizava o uso de um barramento de endereços separado (a Intel era principalmente uma fabricante de DRAM na época).

Dois anos depois, a Intel lançou o 8080, empregando os novos encapsulamentos DIL de 40 pinos originalmente desenvolvidos para circuitos integrados de calculadoras, permitindo um barramento de endereços separado. Ele possuía um conjunto de instruções expandido, compatível em termos de código-fonte (não binário) com o 8008,[6] e também incluía algumas instruções de 16 bits para facilitar a programação. O dispositivo 8080 foi eventualmente substituído pelo 8085 (1977), baseado em carga de depleção, que utilizava uma única fonte de alimentação de +5 V em vez das três tensões de operação diferentes dos chips anteriores.[nota 3] Outros microprocessadores de 8 bits bastante conhecidos que surgiram durante esses anos são o Motorola 6800 (1974), o General Instruments PIC16X (1975), o MOS Technology 6502 (1975), o Zilog Z80 (1976) e o Motorola 6809 (1978).

O primeiro projeto x86

O projeto 8086 teve início em maio de 1976[7] e foi originalmente concebido como um substituto temporário para o ambicioso e atrasado projeto iAPX 432. Foi uma tentativa de desviar a atenção dos processadores de 16 e 32 bits de outros fabricantes — Motorola, Zilog e National Semiconductor — que estavam em desenvolvimento há menos tempo.

Embora o 8086 fosse um microprocessador de 16 bits, ele utilizava uma arquitetura similar à dos microprocessadores de 8 bits da Intel (8008, 8080 e 8085). Isso permitiu que programas em linguagem assembly escritos em 8 bits migrassem sem problemas.[8] Novas instruções e recursos — como inteiros com sinal, endereçamento base + deslocamento e operações autorrepetíveis — foram adicionados. Instruções foram incluídas para auxiliar a compilação do código-fonte de funções aninhadas na família de linguagens ALGOL, incluindo Pascal e PL/M. De acordo com o arquiteto principal Stephen P. Morse, isso foi resultado de uma abordagem mais centrada em software. Outras melhorias incluíram instruções de microcódigo para as instruções de multiplicação e divisão em linguagem assembly. Os projetistas também previram coprocessadores, como o 8087 e o 8089, portanto a estrutura do barramento foi projetada para ser flexível.

A primeira revisão do conjunto de instruções e da arquitetura de alto nível ficou pronta após cerca de três meses e, como quase nenhuma ferramenta CAD foi utilizada, quatro engenheiros e 12 projetistas de layout trabalharam simultaneamente no chip.[nota 4] O 8086 levou pouco mais de dois anos da concepção ao produto funcional, o que era considerado rápido para um projeto complexo na década de 1970.

O 8086 foi sequenciado[nota 5] usando uma combinação de lógica aleatória[9] e microcódigo, e implementado com circuitos nMOS de carga de depleção, com aproximadamente 20.000 transistores ativos (29.000 considerando todos os locais de ROM e PLA). Em pouco tempo, a produção foi transferida para um novo processo de fabricação nMOS refinado, chamado HMOS (sigla em inglês para High Performance MOS), que a Intel desenvolveu originalmente para a fabricação de produtos de memória RAM estática de alta velocidade.[nota 6] A isso se seguiram as versões HMOS-II, HMOS-III e, eventualmente, uma versão CMOS totalmente estática para dispositivos alimentados por bateria, fabricada usando os processos CHMOS da Intel.[nota 7] O chip original media 33 mm² e a menor dimensão dos elementos era de 3,2 μm.

A arquitetura foi definida por Stephen P. Morse, com alguma ajuda de Bruce Ravenel (o arquiteto do 8087) no refinamento das revisões finais. O projetista lógico Jim McKevitt e John Bayliss foram os engenheiros principais da equipe de desenvolvimento de hardware,[nota 8] e Bill Pohlman foi o gerente do projeto. O legado do 8086 permanece presente no conjunto de instruções básicas dos computadores pessoais e servidores atuais; o 8086 também emprestou seus dois últimos dígitos para versões posteriores e estendidas do projeto, como o Intel 286 e o Intel 386, que eventualmente ficaram conhecidos como a família x86. Além disso, o ID de fornecedor PCI para dispositivos de sistema produzidos pela Intel, é 8086.[10]

Detalhes

Barramentos e operação

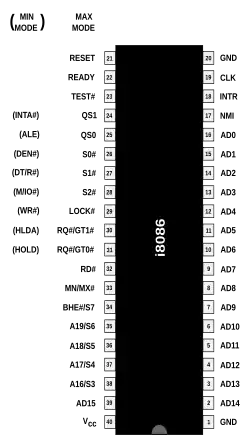

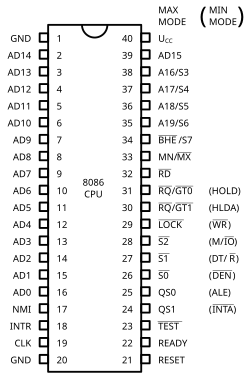

Todos os registradores internos, bem como os barramentos de dados internos e externos, têm 16 bits de largura, o que estabeleceu firmemente a identidade de "microprocessador de 16 bits" do 8086. Um barramento de endereço externo de 20 bits fornece um espaço de endereço físico de 1 MiB (220 = 1.048.576 x 1 byte). Este espaço de endereçamento é gerenciado por meio de "segmentação" de memória interna. O barramento de dados é multiplexado com o barramento de endereços para que todas as linhas de controle caibam em um encapsulamento DIP padrão de 40 pinos. Ele fornece um barramento de endereços de E/S de 16 bits, suportando 64 KB de espaço de E/S separado. O espaço de endereçamento linear máximo é limitado a 64 KB, simplesmente porque os registradores internos de endereço/índice têm apenas 16 bits de largura. A programação em limites de memória de 64 KB envolve o ajuste dos registradores de segmento (veja abaixo); essa dificuldade existiu até que a arquitetura 80386 introduziu registradores mais largos, de 32 bits (o hardware de gerenciamento de memória do 80286 não ajudou nesse aspecto, já que seus registradores ainda têm apenas 16 bits de largura).

Modos de hardware do 8086

Alguns dos pinos de controle, que transportam sinais essenciais para todas as operações externas, têm mais de uma função, dependendo se o dispositivo está operando no modo mínimo ou máximo. O primeiro modo destina-se a pequenos sistemas com um único processador, enquanto o segundo é para sistemas médios ou grandes que utilizam mais de um processador (uma espécie de modo multiprocessador). O modo máximo é necessário ao usar um coprocessador 8087 ou 8089. A tensão no pino 33 (MN/MX) determina o modo. Alterar o estado do pino 33 altera a função de outros pinos, a maioria dos quais relacionados à forma como a CPU gerencia o barramento (local).[nota 9] O modo geralmente é definido no circuito e, portanto, não pode ser alterado por software. O funcionamento desses modos é descrito em termos de diagramas de temporização nos manuais e folhas de dados da Intel. No modo mínimo, todos os sinais de controle são gerados pelo próprio 8086.

Registradores e instruções

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

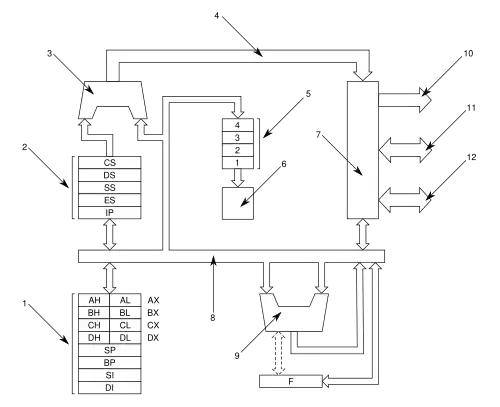

O 8086 possui oito registradores mais ou menos gerais de 16 bits (incluindo o ponteiro de pilha, mas excluindo o ponteiro de instrução, o registrador de flag e os registradores de segmento). Quatro deles, AX, BX, CX, DX, também podem ser acessados como pares de registradores de 8 bits (veja a figura), enquanto os outros quatro, SI, DI, BP, SP, são apenas de 16 bits.[11]

Devido a uma codificação compacta inspirada em processadores de 8 bits, a maioria das instruções são operações de um ou dois endereços, o que significa que o resultado é armazenado em um dos operandos. No máximo um dos operandos pode estar na memória, mas esse operando na memória também pode ser o destino, enquanto o outro operando, a origem, pode ser registrador ou imediato. Muitas vezes, um único local de memória também pode ser usado como origem e destino, o que, entre outros fatores, contribui ainda mais para uma densidade de código comparável (e muitas vezes melhor que) à maioria das máquinas de oito bits da época.

O grau de generalidade da maioria dos registros é muito maior do que no 8080 ou 8085. No entanto, os registros 8086 eram mais especializados do que na maioria dos minicomputadores contemporâneos e também são usados implicitamente por algumas instruções. Embora perfeitamente sensível para o programador assembly, isso torna a alocação de registros para compiladores mais complicada em comparação com processadores mais ortogonais de 16 e 32 bits da época, como o PDP-11, VAX, 68000, 32016, etc. Por outro lado, sendo mais regulares do que os microprocessadores de 8 bits bastante minimalistas, mas onipresentes, como o 6502, 6800, 6809, 8085, MCS-48, 8051 e outras máquinas contemporâneas baseadas em acumuladores, é significativamente mais fácil construir um gerador de código eficiente para a arquitetura 8086.

Outro fator para isso é que o 8086 também introduziu algumas instruções novas (não presentes no 8080 e 8085) para melhor suportar linguagens de programação de alto nível baseadas em pilha, como Pascal e PL/M; algumas das instruções mais úteis são push mem-op, e ret size, apoiando diretamente a "convenção de chamada Pascal". (Vários outros, como push immed e enter, foram adicionados nos processadores 80186, 80286 e 80386 subsequentes.)

Uma pilha de 64 KB (um segmento) crescendo em direção a endereços mais baixos é suportada em hardware; palavras de 16 bits são colocadas na pilha e o topo da pilha é apontado por SS:SP. Existem 256 interrupções, que podem ser invocadas tanto por hardware quanto por software. As interrupções podem ser colocadas em cascata, usando a pilha para armazenar os endereços de retorno.

O 8086 possui 64 K de espaço de porta de E/S de 8 bits (ou alternativamente 32 K de palavras de 16 bits).[12]

Flags

O 8086 possui um registrador de flags de 16 bits. Nove dessas flags de código de condição estão ativas e indicam o estado atual do processador: Flag de Transporte (CF), Flag de Paridade (PF), Flag de Transporte Auxiliar (AF), Flag de Zero (ZF), Flag de Sinal (SF), Flag de Armadilha (TF), Flag de Interrupção (IF), Flag de Direção (DF) e Flag de Overflow (OF). Também conhecido como palavra-chave de status, o layout do registro de flags é o seguinte:[13][14]

| Bit | 15-12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Flag | OF | DF | IF | TF | SF | ZF | AF | PF | CF |

Segmentação

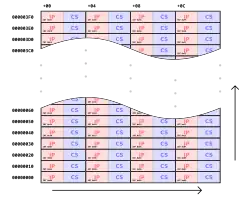

Existem também quatro registradores de segmentação de 16 bits (ver figura) que permitem à CPU 8086 acessar um megabyte de memória de uma maneira incomum. Em vez de concatenar o registrador de segmento com o registrador de endereço, como na maioria dos processadores cujo espaço de endereçamento excede o tamanho de seus registradores, o 8086 desloca o segmento de 16 bits quatro bits para a esquerda antes de adicioná-lo ao deslocamento de 16 bits (16 × segmento + deslocamento), produzindo assim um endereço externo (ou efetivo ou físico) de 20 bits a partir do par segmento:deslocamento de 32 bits. Como resultado, qualquer endereço externo poderia ser referenciado por até 212 = 4096 pares diferentes de segmento:deslocamento.[15]

0110 1000 1000 01110000

|

Segmento, | 16 bits, deslocados 4 bits para a esquerda (ou multiplicados por 0x10) |

+ 1011 0100 1010 1001

|

Deslocamento (offset), | 16 bits |

|

||

0111 0011 1101 0001 1001

|

Endereço, | 20 bits |

Embora considerado complicado e trabalhoso por muitos programadores, este esquema também tem vantagens; um programa pequeno (menos de 64 KB) pode ser carregado a partir de um deslocamento fixo (como 0000) em seu próprio segmento,[14] evitando a necessidade de relocação, com no máximo 15 bytes de desperdício de alinhamento.

Os compiladores para a família 8086 geralmente suportam dois tipos de ponteiro: near ("perto") e far ("longe"). Os ponteiros near são deslocamentos de 16 bits implicitamente associados ao segmento de código ou dados do programa e, portanto, só podem ser usados em partes de um programa pequenas o suficiente para caber em um único segmento. Ponteiros far são pares de segmento:deslocamento de 32 bits que se resolvem em endereços externos de 20 bits. Alguns compiladores também suportam ponteiros huge ("enorme"), que são semelhantes a ponteiros far, exceto que a aritmética de ponteiros em um ponteiro huge o trata como um ponteiro linear de 20 bits, enquanto a aritmética de ponteiros em um ponteiro far dá a volta completa dentro de seu deslocamento de 16 bits sem acessar a parte do segmento do endereço.

Para evitar a necessidade de especificar ponteiros near e far em inúmeros ponteiros, estruturas de dados e funções, os compiladores também suportam "modelos de memória" que especificam tamanhos de ponteiro padrão. Os modelos tiny (máximo de 64 KB), small (máximo de 128 KB), compact (dados > 64 KB), medium (código > 64 KB), large (código e dados > 64 KB) e huge (arrays individuais > 64 KB) abrangem combinações práticas de ponteiros near, far e huge para código e dados. O modelo de memória compact significa que o código e os dados são compartilhados em um único segmento, assim como na maioria dos processadores de 8 bits, e pode ser usado para criar arquivos .com, por exemplo. Bibliotecas pré-compiladas geralmente vêm em diversas versões compiladas para diferentes modelos de memória.

Segundo Morse et al.,[16] os projetistas chegaram a cogitar o uso de um deslocamento de 8 bits (em vez de 4 bits) para criar um espaço de endereçamento físico de 16 MB. No entanto, como isso forçaria os segmentos a começarem em limites de 256 bytes, e 1 MB era considerado muito grande para um microprocessador por volta de 1976, a ideia foi descartada. Além disso, não havia pinos suficientes disponíveis em um encapsulamento de baixo custo de 40 pinos para os quatro pinos adicionais do barramento de endereços.

Em princípio, o espaço de endereçamento da série x86 poderia ter sido expandido em processadores posteriores aumentando o valor do deslocamento, desde que os aplicativos obtivessem seus segmentos do sistema operacional e não fizessem suposições sobre a equivalência de diferentes pares segmento:deslocamento.[nota 10] Na prática, o uso de ponteiros huge e mecanismos semelhantes era generalizado, e o endereçamento plano de 32 bits, possibilitado pelos registradores de deslocamento de 32 bits no 80386, acabou por estender o alcance de endereçamento limitado de uma forma mais geral.

O fluxo de instruções é buscado na memória em palavras e endereçado internamente pelo processador até o nível de byte, conforme necessário. Um mecanismo de enfileiramento do fluxo de instruções permite que até 6 bytes do fluxo de instruções sejam enfileirados enquanto aguardam decodificação e execução. A fila funciona como um buffer FIFO (primeiro a entrar, primeiro a sair), do qual a Unidade de Execução (UE) extrai bytes de instrução conforme necessário. Sempre que houver espaço para pelo menos dois bytes na fila, a Unidade de Interface de Blocos (UIB) tentará um ciclo de busca de palavra na memória. Se a fila estiver vazia (após uma instrução de desvio, por exemplo), o primeiro byte na fila fica imediatamente disponível para a UE.[17]

Adaptação de software antigo

Programas pequenos podiam ignorar a segmentação e usar apenas endereçamento de 16 bits. Isso permite que softwares de 8 bits sejam facilmente adaptados para o 8086. Os autores da maioria das implementações de DOS aproveitaram isso, fornecendo uma API muito semelhante ao CP/M, além de incluir o formato de arquivo executável .com simples, idêntico ao do CP/M. Isso foi importante quando o 8086 e o MS-DOS eram novidades, pois permitiu que muitos aplicativos CP/M (e outros) existentes fossem disponibilizados rapidamente, facilitando muito a aceitação da nova plataforma.[18][19]

Interrupções

As interrupções no 8086 podem ser iniciadas por software ou por hardware. As interrupções são chamadas longas que também salvam o estado do processador. As rotinas de interrupção normalmente terminam com uma instrução IRET. Todas as interrupções possuem um número de interrupção de 8 bits associado a elas. Esse número é usado para localizar um segmento:deslocamento em uma tabela de vetores de interrupção de 256 elementos armazenada nos endereços 0-3FFH. Quando qualquer tipo de interrupção é encontrada, o estado do processador é atualizado, CS e IP são atualizados e o número da interrupção é multiplicado por quatro para indexar um novo endereço de execução que é carregado da tabela de vetores.[20]

Existem três tipos de instruções de interrupção de software: INT n, INTO e uma INT 3 de um único byte usada para depuração.[20]

Existem dois tipos de interrupções de hardware: mascaráveis e não mascaráveis.

Interrupções não mascaráveis têm prioridade maior que interrupções mascaráveis. Elas não podem ser desabilitadas pela habilitação de interrupção. Uma transição de nível baixo para alto no pino NMI essencialmente causa a execução de uma INT 2.

As interrupções mascaráveis são habilitadas e desabilitadas pelas instruções STI e CLI, respectivamente. Quando o sinal INTR é acionado por um dispositivo de hardware, o 8086 aciona o sinal INTA duas vezes, lendo um número de interrupção de 8 bits do barramento. Esse número é multiplicado por quatro para apontar para o endereço da rotina de serviço de interrupção associada na tabela de vetores. As interrupções mascaráveis são desativadas quando INTA é ativado, mas são reativadas ao executar a instrução IRET no final da rotina de serviço de interrupção.[20][17]

Código de exemplo

O seguinte código-fonte em assembly 8086 é para uma sub-rotina chamada _strtolower que copia uma string de caracteres ASCIIZ terminada em nulo de um local para outro, convertendo todos os caracteres alfabéticos em minúsculos. A string é copiada um byte (caractere de 8 bits) por vez.

0000 0000 55 0001 89 E5 0003 56 0004 57 0005 8B 75 06 0008 8B 7D 04 000B FC 000C AC 000D 3C 41 000F 7C 06 0011 3C 5A 0013 7F 02 0015 04 20 0017 AA 0018 08 C0 001A 75 F0 001C 5F 001D 5E 001E 5D 001F C3 001F |

; _strtolower:

; Copia uma string ASCII terminada em nulo, convertendo

; todos os caracteres alfabéticos em minúsculas.

; ES=DS

; Parâmetros da pilha de entrada

; [SP+4] = src, Endereço da string de origem

; [SP+2] = dst, Endereço da string de destino

; [SP+0] = Endereço de devolução

;

_strtolower proc

push bp ;Set up the call frame

mov bp,sp

push si

push di

mov si,[bp+6] ;Set si = src (+2 due to push bp)

mov di,[bp+4] ;Set di = dst

cld ;string direction ascending

loop: lodsb ;Load al from [si], inc si

cmp al,'A' ;If al < 'A',

jl copy ; skip conversion

cmp al,'Z' ;If al > 'Z',

jg copy ; skip conversion

add al,'a'-'A' ;Convert al to lowercase

copy: stosb ;Store al to es:[di], inc di

or al,al ;If al <> 0,

jne loop ; repeat the loop

done: pop di ;restore di and si

pop si

pop bp ;Restore the prev call frame

ret ;Return to caller

end proc

|

O código de exemplo usa o registrador BP (ponteiro base) para estabelecer uma pilha de chamada, uma área na pilha que contém todos os parâmetros e variáveis locais para a execução da sub-rotina. Esse tipo de convenção de chamada suporta código reentrante e recursivo e tem sido usado por linguagens do tipo ALGOL desde o final da década de 1950. Assume-se um modelo de memória plana, especificamente, que os segmentos DS e ES endereçam a mesma região de memória.

Desempenho

Embora parcialmente ofuscado por outras opções de design neste chip específico, o endereço multiplexado e os barramentos de dados limitam ligeiramente o desempenho; as transferências de quantidades de 16 ou 8 bits são feitas em um ciclo de acesso à memória de quatro clocks, que é mais rápido em quantidades de 16 bits, embora mais lento em quantidades de 8 bits, em comparação com muitas CPUs contemporâneas baseadas em 8 bits. Como as instruções variam de um a seis bytes, a busca e a execução são feitas simultaneamente e desacopladas em unidades separadas (como permanece nos processadores x86 atuais): a Bus Interface Unit ("unidade de interface de barramento") alimenta o fluxo de instruções para a unidade de execução através de uma fila de pré-busca de 6 bytes (uma forma de segmentação fracamente acoplada), acelerando as operações em registradores e imediatos, enquanto as operações de memória se tornaram mais lentas (quatro anos depois, esse problema de desempenho foi corrigido com o 80186 e o 80286). No entanto, a arquitetura completa (em vez de parcial) de 16 bits com uma ALU de largura total significava que instruções aritméticas de 16 bits agora podiam ser executadas com um único ciclo ALU (em vez de dois, via transporte interno, como no 8080 e 8085), acelerando consideravelmente essas instruções. Combinado com ortogonalizações de operações versus tipos de operandos e modos de endereçamento, bem como outras melhorias, isso tornou o ganho de desempenho em relação ao 8080 ou 8085 bastante significativo, apesar dos casos em que os chips mais antigos podem ser mais rápidos (veja abaixo).

| instrução | registro-registro | registro imediato | registro-memória | memória-registro | memória-imediato |

|---|---|---|---|---|---|

| mov | 2 | 4 | 8+EA | 9+EA | 10+EA |

| ALU | 3 | 4 | 9+EA, | 16+EA, | 17+EA |

| salto | registro ≥ 11 ; rótulo ≥ 15 ; condição, rótulo ≥ 16 | ||||

| multiplicação inteira | 70~160 (dependendo dos dados do operando, bem como do tamanho) incluindo qualquer EA | ||||

| divisão inteira | 80~190 (dependendo dos dados do operando, bem como do tamanho) incluindo qualquer EA | ||||

- EA = tempo para calcular o endereço efetivo, variando de 5 a 12 ciclos.

- Os tempos são o melhor caso, dependendo do status da pré-busca, alinhamento das instruções e outros fatores.

Como pode ser visto nessas tabelas, as operações em registradores e imediatos eram rápidas (entre 2 e 4 ciclos), enquanto as instruções e saltos de operandos de memória eram bastante lentos; os saltos levaram mais ciclos do que nos mais simples 8080 e 8085, e o 8088 (usado no IBM PC) foi adicionalmente prejudicado por seu barramento mais estreito. Havia duas razões principais pelas quais a maioria das instruções relacionadas à memória eram lentas:

- Unidades de busca e execução fracamente acopladas são eficientes para pré-busca de instruções, mas não para saltos e acesso aleatório a dados (sem medidas especiais).

- Nenhum somador de cálculo de endereço dedicado foi fornecido; as rotinas de microcódigo tiveram que usar a ALU principal para isso (embora houvesse um segmento dedicado + somador de deslocamento).

No entanto, o desempenho do acesso à memória foi drasticamente aprimorado com a próxima geração de CPUs da família 8086 da Intel. O 80186 e o 80286 tinham hardware de cálculo de endereço dedicado, economizando muitos ciclos, e o 80286 também tinha endereços e barramentos de dados separados (não multiplexados).

Ponto flutuante

O 8086/8088 pode ser conectado a um coprocessador matemático para adicionar desempenho de ponto flutuante baseado em hardware/microcódigo. O Intel 8087 foi o coprocessador matemático padrão para o 8086 e 8088, operando em números de 80 bits. Fabricantes como Cyrix (compatível com 8087) e Weitek (não compatível com 8087) eventualmente criaram coprocessadores de ponto flutuante de alto desempenho que competiam com o 8087.[22]

Versões do chip

A frequência do clock foi originalmente limitada a 5 MHz,[nota 11] mas as últimas versões em HMOS foram especificadas para 10 MHz. As versões HMOS-III e CMOS foram fabricadas por muito tempo (pelo menos na década de 1990) para sistemas embarcados, embora seu sucessor, o 80186/80188 (que inclui alguns periféricos no chip), tenha sido mais popular para uso embarcado.

O 80C86, a versão CMOS do 8086, foi usado em muitos computadores portáteis e sistemas embarcados, incluindo o GridPad, Toshiba T1200, HP 110 e, finalmente, o Lunar Prospector de 1998–1999.

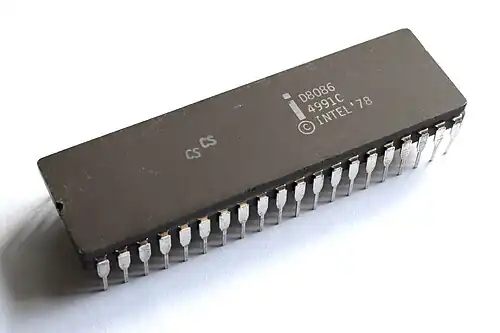

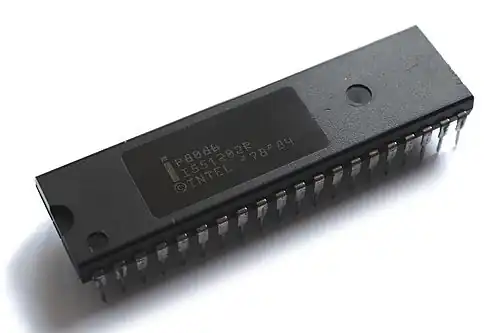

Para o acondicionamento, o Intel 8086 estava disponível em variações DIP de cerâmica e plástico.

-

Uma variante cerâmica D8086

Uma variante cerâmica D8086 -

Uma variante P8086 de plástico

Uma variante P8086 de plástico

Notas

- ↑ Menos buffers TTL, latches e multiplexadores (embora a quantidade de lógica TTL não tenha sido drasticamente reduzida). Também permite o uso de CIs baratos da família 8080, onde o 8254 CTC, o 8255 PIO e o 8259 PIC foram usados no projeto do IBM PC. Além disso, simplifica o layout da placa de circuito impresso e barateia o custo das placas, além de exigir menos chips de DRAM (de 1 ou 4 bits de largura).

- ↑ usando carga de aprimoramento lógica PMOS (requerendo 14 V, alcançando compatibilidade TTL tendo VCC em +5 V e VDD em −9 V).

- ↑ Possibilitado pela lógica nMOS de carga de depleção (o 8085 foi posteriormente fabricado usando processamento HMOS, assim como o 8086).

- ↑ Utilizando rubylith, quadros de luz, réguas, apagadores elétricos e um digitalizador (de acordo com Jenny Hernandez, membro da equipe de design do 8086, em uma declaração feita na página da Intel por ocasião de seu 25º aniversário).

- ↑ O 8086 utilizava menos microcódigo do que muitos projetos concorrentes, como o MC68000 e outros.

- ↑ Memórias RAM estáticas rápidas com tecnologia MOS (tão rápidas quanto as RAMs bipolares) foram um produto importante para a Intel durante esse período.

- ↑ CHMOS é o nome que a Intel dá aos circuitos CMOS fabricados usando etapas de processamento muito semelhantes às do HMOS.

- ↑ Outros membros da equipe de design foram Peter A. Stoll e Jenny Hernandez.

- ↑ Os computadores IBM PC e PC/XT utilizam um processador Intel 8088 em modo máximo, o que permite que a CPU trabalhe com um coprocessador 8087 opcional instalado no soquete do coprocessador matemático na placa-mãe do PC ou PC/XT. (O PC e o PC/XT podem exigir o modo máximo por outros motivos, como, por exemplo, para suportar o controlador DMA.)

- ↑ Alguns clones do 80186 alteraram o valor de deslocamento, mas nunca foram comumente usados em computadores desktop.

- ↑ (O IBM PC usou 4,77 MHz, 4/3 da frequência NTSC padrão do sinal color burst)

Referências

- ↑ «Microprocessor Hall of Fame» (em inglês). Intel. Consultado em 11 de agosto de 2007. Cópia arquivada em 6 de julho de 2007

- ↑ iAPX 286 Programmer's Reference (PDF) (em inglês). [S.l.]: Intel. 1983. p. 1-1

- ↑ a b «Happy Birthday, 8086: Limited-Edition 8th Gen Intel Core i7-8086K Delivers Top Gaming Experience». Intel Newsroom (Nota de imprensa) (em inglês). Intel. 5 de junho de 2018. Cópia arquivada em 12 de fevereiro de 2023

- ↑ Šojat, Z.; Skala, K.; Rogina, B.M.; Škoda, P.; Sović, I. (2016). «Implementation of Advanced Historical Computer Architectures §2.5 Microprocessors». In: Szewczyk, R.; Kaštelan, I.; Temerinac, M.; Barak, M.; Sruk, V. Embedded Engineering Education (em inglês). [S.l.]: Springer. ISBN 978-3-319-27540-6

- ↑ «The 8088 Processor». timeline.intel.com (em inglês). Intel. Consultado em 26 de janeiro de 2025

- ↑ «8080 family». CPU World (em inglês)

- ↑ «Birth of a standard: The Intel 8086 microprocessor turns 40 today». PCWorld (em inglês). Consultado em 8 de março de 2025

- ↑ Scanlon, Leo J. (1988). 8086/8088/80286 assembly language (em inglês). [S.l.]: Brady Books. p. 12. ISBN 978-0-13-246919-7.

[…] O 8086 é compatível em termos de software com o 8080 a nível de linguagem assembly. […]

- ↑ Geiger, Randall L.; Allen, Phillip E.; Strader, Noel R. (1990). «Random Logic vs. Structured Logic Forms». VLSI design techniques for analog and digital circuits (em inglês). [S.l.]: McGraw-Hill. 779 páginas. ISBN 0-07-023253-9 — Ilustração do uso de "aleatório" para descrever a lógica de controle da CPU.

- ↑ «PCI\VEN_8086 - Intel Corporation». Device Hunt (em inglês). 4 de agosto de 2025. Consultado em 14 de agosto de 2025

- ↑ Morse, Stephen P. (1982). The 8086/8088 Primer: An Introduction to Their Architecture, System Design, and Programming (PDF) (em inglês) 2. ed. Rochelle Park, N. J: Hayden Book Co. ISBN 0-8104-6255-9. Consultado em 23 de novembro de 2025

- ↑ Shaikh, Jishan (28 de maio de 2022). «8086 Microprocessor Cheatsheet» (PDF) (em inglês). Consultado em 31 de janeiro de 2026

- ↑ Intel Corporation (1983). IAPX 86, 88, 186, and 188 user's manual: programmer's reference (em inglês). [S.l.]: Intel. pp. 3–5. ISBN 978-0835930352. OCLC 11091251

- ↑ a b «Arquitetura do microprocessador 8086» (PDF). UNICAMP. Consultado em 1 de fevereiro de 2026

- ↑ Sedory, Daniel B. «The Segment:Offset Addressing Scheme». thestarman.pcministry.com (em inglês). Consultado em 6 de março de 2025

- ↑ Morse, Stephen P.; Ravenel, Bruce W; Mazor, Stanley; Pohlman, William B. (outubro de 1980). «Intel Microprocessors: 8008 to 8086». IEEE Computer (em inglês). 13 (10): 42–60. doi:10.1109/MC.1980.1653375

- ↑ a b «8086 16-BIT HMOS Processor datasheet» (PDF) (em inglês). Intel. Consultado em 26 de novembro de 2021. Cópia arquivada (PDF) em 26 de novembro de 2021

- ↑ «CP/M-86 Compatibility Guide For CP/M-80 Users» (em inglês). Pacific Grove, Califórnia: Digital Research. 21 de outubro de 1980. Consultado em 5 de fevereiro de 2026

- ↑ List, Jenny (13 de junho de 2021). «TRANSLATE YOUR CP/M CODE TO 8086, AND LEAVE THE 1970S BEHIND!». Hackaday (em inglês). Consultado em 5 de fevereiro de 2026

- ↑ a b c Moraes, Raimes (4 de maio de 2010). UFSC, ed. «Microprocessadores» (PDF). Consultado em 6 de fevereiro de 2026

- ↑ Microsoft Macro Assembler 5.0 Reference Manual (em inglês). [S.l.]: Microsoft Corporation. 1987.

As temporizações e codificações neste manual são usadas com permissão da Intel e vêm das seguintes publicações: Intel Corporation. iAPX 86, 88, 186 and 188 User's Manual, Programmer's Reference, Santa Clara, Calif. 1986.

(Da mesma forma para iAPX 286, 80386, 80387.) - ↑ «Math Coprocessors». DOS Days (em inglês). Consultado em 8 de fevereiro de 2026

Ligações externas

- «O microprocessador Intel 8086 de 1978». MCC. 8 de junho de 2022. Consultado em 27 de janeiro de 2026